简介:本教程由浅入深、循序渐进,带领零基础的学生逐渐掌握Verilog基本语法、数字电路基础、状态机编程思路、Vivado基本使用方法、电路原理图基本阅读技巧和FPGA基本编程技巧、高速接口、项目实战等。通过本教程的学习与实战,学生真正可以进入FPGA的精彩世界。

- 课程详情

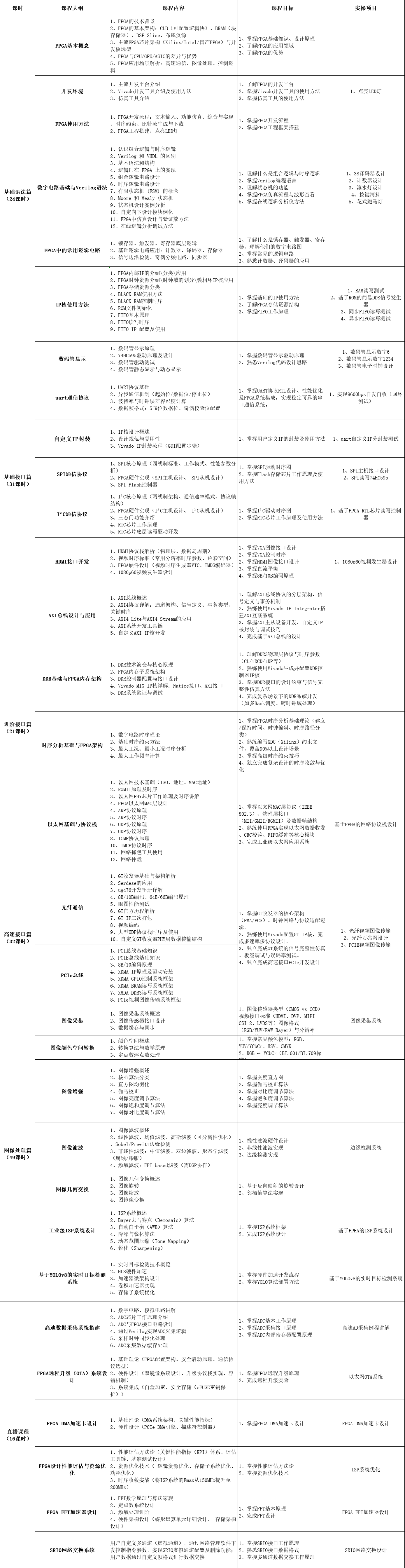

- 课程目录

课程介绍:

1、培养目标:成为具备实战型的FPGA工程师(初级);

2、课程学时:100天 ;

3、人数限制:30人 ;

4、招生对象:0零基础学习(理工科类相关专业);

5、推荐就业:就业推荐协议+模拟面试+简历优化+企业内推;

项目实战:

采用赛灵思原厂+自主研发拓展板;

1、基于ZYNQ7000的虚拟示波器;

2、基于AI的图像识别系统;

3、实时图像处理及存储系统;

项目包括:(DDS信号发生器(纯verilog)、虚拟示波器(纯verilog)、以太网视频传输(纯verilog)、UBS3.0视频图像传输(纯verilog)、运动目标检测(纯verilog)、图像存储系统(纯verilog)、PCIE视频图像传输(纯verilog)、光纤视频图像传输(纯verilog))

课程大纲:

讲师介绍:

周老师:

中国地质大学(武汉),通信工程学士学位,中国科学院大学,硕博连读,工学博士学位,德国重离子研究中心(GSI),FAIR 数据获取,博士后,研究方向:数据获取、电子学、工业测控、层析成像等;

陈老师:

电子科技大学通信学院 博士后,电子科技大学 电子工程学院 电磁场与微波技术 工学博士;四川大学 电子信息学院 无线电物理 理学硕士,研究方向:射频、FPGA高性能计算等;

王老师:

本科毕业于电子科技大学(集成电路设计与集成系统专业),硕士毕业于美国特拉华大学,博士毕业于澳大利亚新南威尔士大学,研究方向:集成电路、光伏等;

课程安排:

授课:全天答疑、线下授课 + 线上直播结合;

扫码添加老师咨询课程!

课表安排

- DAY 1 |

就业咨询

时长

- DAY 2 |

FPGA是什么

时长

- DAY 3 |

FPGA发展史

时长

- DAY 4 |

FPGA应用场景

时长

- DAY 5 |

vivado使用(实操),FPGA开发流程

时长

- DAY 6 |

verilog基础语法(模块结构、端口、变量、常量、标识符、赋值语句)

时长

- DAY 7 |

数字电路基础(逻辑门、竞争与冒险、电平标准、触发器)

时长

- DAY 8 |

verilog进阶语法(always语句、case语句、if语句、begin end、阻塞赋值与非阻塞赋值)

时长

- DAY 9 |

查找表结构

时长

- DAY 10 |

计数器(实操)

时长

- DAY 11 |

分频器(实操)

时长

- DAY 12 |

跑马灯实验(实操)

时长

- DAY 13 |

状态机(含义、原理、状态机分类、实现方式)

时长

- DAY 14 |

状态机实现按键消抖(实操、模块化设计)

时长

- DAY 15 |

数码管(含义、显示原理、原理图连线)

时长

- DAY 16 |

译码器

时长

- DAY 17 |

数码管静态显示1234(实操)

时长

- DAY 18 |

动态显示原理

时长

- DAY 19 |

数码管计数器(实操)

时长

- DAY 20 |

时长

- DAY 21 |

可综合不可综合语句

时长

- DAY 22 |

仿真语法

时长

- DAY 23 |

仿真(仿真含义、仿真分类)

时长

- DAY 24 |

时序图含义

时长

- DAY 25 |

Simulation仿真教程(按键消抖)

时长

- DAY 26 |

74HC595手册阅读

时长

- DAY 27 |

74HC595驱动原理

时长

- DAY 28 |

点阵屏静态显示(实操)

时长

- DAY 29 |

ILA含义

时长

- DAY 30 |

vivado逻辑分析仪使用(ip core、mark debug、原理图标记)

时长

- DAY 31 |

捕捉按键有效信号(实操)

时长

- DAY 32 |

时钟抖动

时长

- DAY 33 |

vivado clocking_wizard原理

时长

- DAY 34 |

vivado clocking_wizard使用

时长

- DAY 35 |

序列发送器

时长

- DAY 36 |

超声波手册阅读

时长

- DAY 37 |

超声波驱动原理(接收端与发射端)

时长

- DAY 38 |

时长

- DAY 39 |

uart的含义

时长

- DAY 40 |

通信方式的分类(异步通信、同步通信)

时长

- DAY 41 |

通信方向的分类(单工、半双工、全双工)

时长

- DAY 42 |

通信数据分类(串行、并行)

时长

- DAY 43 |

uart通信协议(uart含义、波特率、起始位、数据位、奇偶校验位、停止位)

时长

- DAY 44 |

uart时序图讲解

时长

- DAY 45 |

状态机讲解

时长

- DAY 46 |

CH340

时长

- DAY 47 |

ram简介(ram介绍、FPGA中的ram资源介绍)

时长

- DAY 48 |

DRAM与BRAM区别

时长

- DAY 49 |

RAM时序图讲解

时长

- DAY 50 |

RAM ip配置讲解

时长

- DAY 51 |

ram uart回环

时长

- DAY 52 |

模块化设计

时长

- DAY 53 |

状态机讲解

时长

- DAY 54 |

FIFO简介

时长

- DAY 55 |

FIFO应用(缓存、异步信号处理)

时长

- DAY 56 |

FIFO时序讲解

时长

- DAY 57 |

FIFO配置(异步FIFO,同步FIFO区别)

时长

- DAY 58 |

FIFO uart回环

时长

- DAY 59 |

模块化设计

时长

- DAY 60 |

状态机讲解

时长

- DAY 61 |

乒乓缓存简介

时长

- DAY 62 |

乒乓缓存应用

时长

- DAY 63 |

pp缓存实现方式(ram,FIFO)

时长

- DAY 64 |

状态机讲解

时长

- DAY 65 |

时长

- DAY 66 |

SPI简介

时长

- DAY 67 |

spi应用

时长

- DAY 68 |

物理层链接(主从连接模式、3线、4线)

时长

- DAY 69 |

协议层(时钟极性、时钟相位、时序图讲解)

时长

- DAY 70 |

状态机讲解(spi主机)

时长

- DAY 71 |

flash写使能指令时序图

时长

- DAY 72 |

模块化设计

时长

- DAY 73 |

状态机讲解

时长

- DAY 74 |

flash写操作时序图

时长

- DAY 75 |

模块化设计

时长

- DAY 76 |

flash读操作时序图

时长

- DAY 77 |

模块化设计

时长

- DAY 78 |

状态机讲解

时长

- DAY 79 |

IIC简介

时长

- DAY 80 |

IIC应用

时长

- DAY 81 |

IIC物理层链接(主从连接模式、上拉电阻)

时长

- DAY 82 |

IIC协议层

时长

- DAY 83 |

IIC时序图讲解(主机)

时长

- DAY 84 |

状态机讲解

时长

- DAY 85 |

EEPROM简介(rom,prom,eprom,eeprom)

时长

- DAY 86 |

EEPROM应用

时长

- DAY 87 |

EEPROM手册阅读

时长

- DAY 88 |

EEPROM读写数据时序

时长

- DAY 89 |

模块化设计

时长

- DAY 90 |

状态机讲解

时长

- DAY 91 |

时长

- DAY 92 |

HDMI简介

时长

- DAY 93 |

HDMI应用

时长

- DAY 94 |

HDMI物理层链接

时长

- DAY 95 |

HDMI接口设计原理(VGA TO HDMI)

时长

- DAY 96 |

TDMS算法编码讲解

时长

- DAY 97 |

流水线设计

时长

- DAY 98 |

TMDS算法实现(实操)

时长

- DAY 99 |

原语介绍

时长

- DAY 100 |

原语的应用

时长

- DAY 101 |

OSERDESE2(并转串)介绍

时长

- DAY 102 |

OSERDESE2讲解

时长

- DAY 103 |

OBUFDS(差分输出)

时长

- DAY 104 |

OBUFDS讲解

时长

- DAY 105 |

HDMI模块化设计

时长

- DAY 106 |

HDMI移动方块设计原理

时长

- DAY 107 |

状态机讲解

时长

- DAY 108 |

HDMI图片显示设计原理

时长

- DAY 109 |

时序约束基本概念解析、IO约束和时钟周期

时长

- DAY 110 |

约束、虚拟时钟和多周期路径约束、约束实例

时长

- DAY 111 |

时长

- DAY 112 |

DDR简介

时长

- DAY 113 |

DDR存储原理

时长

- DAY 114 |

MIG接口简介

时长

- DAY 115 |

MIG接口历程讲解

时长

- DAY 116 |

MIG控制器时序

时长

- DAY 117 |

MIG控制器编写

时长

- DAY 118 |

MIG控制器仿真

时长

- DAY 119 |

MIG控制器调试

时长

- DAY 120 |

时长

- DAY 121 |

以太网基础

时长

- DAY 122 |

MAC控制器简介

时长

- DAY 123 |

RGMII接口时序

时长

- DAY 124 |

原语介绍

时长

- DAY 125 |

RGMII接口实现

时长

- DAY 126 |

以太网数据包

时长

- DAY 127 |

arp协议简介

时长

- DAY 128 |

arp数据包分析

时长

- DAY 129 |

arp数据包实现

时长

- DAY 130 |

上位机调试抓包

时长

- DAY 131 |

arp调试

时长

- DAY 132 |

UDP简介

时长

- DAY 133 |

UDP数据包分析

时长

- DAY 134 |

UDP数据包实现

时长

- DAY 135 |

ICMP简介

时长

- DAY 136 |

ICMP数据包分析

时长

- DAY 137 |

ICMP实现

时长

- DAY 138 |

三速以太网测试

时长

- DAY 139 |

时长

- DAY 140 |

通用串行总线接口,支持高速数据传输,用于连接外部设备

时长

- DAY 141 |

USB简介

时长

- DAY 142 |

USB数据包

时长

- DAY 143 |

USB令牌包

时长

- DAY 144 |

USB实现方式介绍

时长

- DAY 145 |

USB核心芯片介绍

时长

- DAY 146 |

USB时序讲解

时长

- DAY 147 |

时长

- DAY 148 |

简介

时长

- DAY 149 |

VS2015安装

时长

- DAY 150 |

WIN10SDK安装

时长

- DAY 151 |

PCIE驱动编译

时长

- DAY 152 |

QT安装

时长

- DAY 153 |

XDMA简介

时长

- DAY 154 |

XDMA配置

时长

- DAY 155 |

PCIE读写例程测试

时长

- DAY 156 |

控制卡介绍

时长

- DAY 157 |

系统框架介绍

时长

- DAY 158 |

FPGA代码编写

时长

- DAY 159 |

数据卡介绍

时长

- DAY 160 |

系统框架介绍

时长

- DAY 161 |

PCIE数据卡DDR3缓存实验

时长

- DAY 162 |

PCIE视频图像采集原理

时长

- DAY 163 |

系统框架介绍

时长

- DAY 164 |

时长

- DAY 165 |

SFP接口介绍

时长

- DAY 166 |

SFP接口测试

时长

- DAY 167 |

IBERT简介

时长

- DAY 168 |

IBERT简介设计

时长

- DAY 169 |

GTP 基本结构

时长

- DAY 170 |

GTP 发送和接收处理流程

时长

- DAY 171 |

GTP 的参考时钟

时长

- DAY 172 |

GTP 发送接口

时长

- DAY 173 |

GTP 接收接口

时长

- DAY 174 |

GTP IP核调用和使用

时长

- DAY 175 |

时长

- DAY 176 |

C语言数据类型及运算式、基本语法、函数、预处理命令、数组、指针、结构体、链表、输入输出

时长

- DAY 177 |

GPIO简介

时长

- DAY 178 |

GPIO寄存器

时长

- DAY 179 |

GPIO例程讲解

时长

- DAY 180 |

点亮EMIO端口LED、EMIO中断、MIO中 断

时长

- DAY 181 |

AXI_GPIO介绍

时长

- DAY 182 |

AXI_GPIO控制原理

时长

- DAY 183 |

时长

- DAY 184 |

中断原理、PL端按键中断

时长

课程概述

课程推荐

学习服务

- 技术大牛直播授课

- 实时学情管理

- 课后作业批改,BUG诊断

- 辅导老师当堂答疑

- 学习规划,专属学习方案